# High Density 3D CMOS Mixed-Signal Opportunities

The **3D-MUSE** project

Univ. of Oslo, CEA/LETI, IDEAS AS, Lund University, ST

Microelectronics, INP Grenoble

Philipp Häfliger hafliger@ifi.uio.no

The 3D-MUSE Project

Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

Conclusion

## The 3D-MUSE Project

Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

Conclusion

System-in-Cube (SinC) Smart Sensor Interfaces (SSI) in Sequential 3D CMOS Technology

The 3D-MUSE Project

## Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

Conclusion

## Bottlenecks for IoT/portable devices

More challenging to scale (power, size, price) than digital electronics:

- mixed signal circuits

- sensors

- communication (antennas)

- energy supply

#### Conclusion:

- Digital electronics is no longer the bottleneck for the IoT.

- The main sales argument for IoT devices is not more processing power/memory

- The main sales argument for IoT devices is the number of ways they can interact with the real world

## Bottlenecks for IoT/portable devices

More challenging to scale (power, size, price) than digital electronics:

- >mixed signal circuits <</p>

- sensors

- communication (antennas)

- energy supply

#### Conclusion:

- Digital electronics is no longer the bottleneck for the IoT.

- The main sales argument for IoT devices is not more processing power/memory

- ► The main sales argument for IoT devices is the number of ways they can interact with the real world

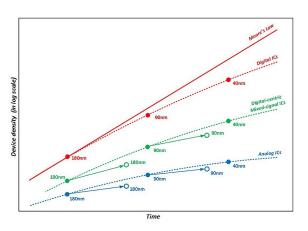

## Analog and Mixed-Signal do not scale according to Moore's Law

Consequence:

While the price per

digital device is

going down with

more adavaned

CMOS technology,

the price per analog

device is actually

going up.

#### courtesy of SiLabs

http://www.embedded-computing.com/processing/

$\verb|the-art-and-science-of-rf-and-mixed-signal-design|$

The 3D-MUSE Project

Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

Conclusion

The 3D-MUSE Project

Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

Conclusion

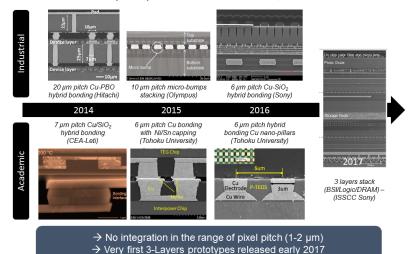

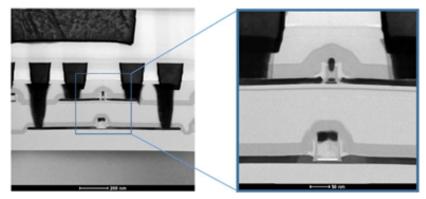

## Parallel 3D integration

## Trans-Silicon Via (TSV) pitch still above $1-2\mu m$

courtesy of CEA/LETI, Grenoble, France

The 3D-MUSE Project

Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

Conclusion

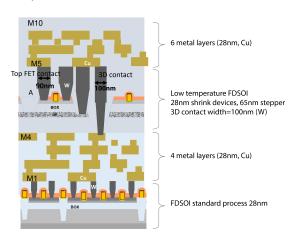

## Sequential 3D integration (1/2)

Inter-Tier Interconnect pitch at 220nm (2017) **5-10x better than SoA, i.e. 25-100x better density** Unique to 3D-MUSE: inter-tier metal.

courtesy of CEA/LETI, Grenoble, France

## Sequential 3D integration (2/2)

courtesy of CEA/LETI, Grenoble, France

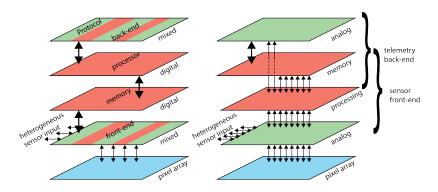

## System-in-Cube vs System-in-Stack

Adavantages in production cost, energy consumption, noise reduction, processing speed

The 3D-MUSE Project

Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

Conclusion

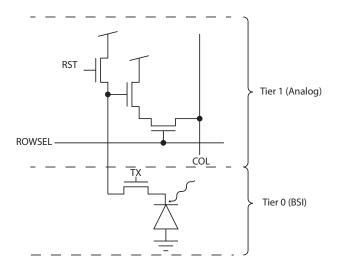

## 3D: BSI and APS

Even closer to 100% fill factor without micro-lens array. 'TSV' in the order of 100nm. Sub-0.8 $^2\mu\text{m}^2$  pixels?

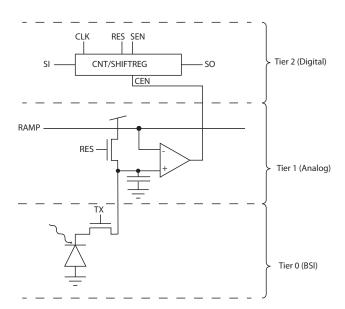

## 3D: BSI and in-pixel ADC

## Micro-Bolometer Arrays

from 'Electro-Thermal Modeling and Experimental Validation of Integrated Microbolometer with ROIC' by Gyungtae Kim et al.

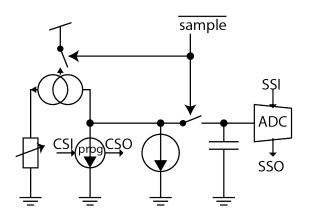

## MBA ROIC Pixel 3DSI Block Diagram

Bolomter ROIC pixel concept: all 'analog' transistors in 65nm top tier all digital in 28nm bottom tier.

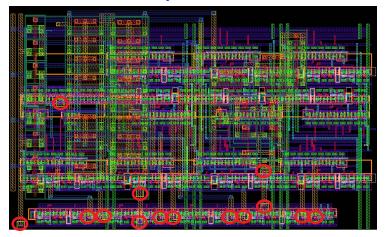

## MBA ROIC Pixel 3DSI Layout

A  $8\mu m \times 13\mu m$  layout of a micro-bolometer array (MBA) 3DSI read-out integrated circuit (ROIC) pixel, FE, 10b ADC, 4b FPN calibration. 14 3D vias: 5 power, 8 calibration bits, 1 comparator output. Connection to MEMS bolometer would be parallel 3D, e.g. Cu-Cu.

## 3D: In general SIMD in a 2D array

(The Neuromorphs have done this for ages in 2D tech with abominable fill-factor)

Processing both in analog or digital domain. For example 2D-convolution (aka: feature maps, CNN, ...), image overlay, or even small general purpose in-pixel processors

The 3D-MUSE Project

Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

#### Conclusion

## Take Home Messages

#### What I told you:

- digital is no longer the scaling bottleneck ...

- ... nor is it the most important sales argument

- e.g. mixed-signal is more challenging to scale, promising better pay off

- multi-process 3DSI is a mixed-signal designer's dream

- real circuits in a volume within reach with many benefits in cost and performance

#### What's next?

- near future developments will probably see a mix of monolithic/sequential and parallel 3D

- appropriate design tools are needed

The 3D-MUSE Project

Mixed-Signal Circuits Scaling

Multi-Process Sequential 3D Integration and System-in-Cube State-of-the-Art Parallel 3D Integration Beyond State-of-the-Art Sequential 3D Integration

Prospects for 2D sensor arrays

Conclusion

#### Contact Information

Philipp Häfliger, hafliger@ifi.uio http://www.3dmuse.eu http://heim.ifi.uio.no/~hafliger/